Можно ли использовать модули оперативной памяти (ОЗУ) от обычного компьютера в сервере? И наоборот? Чем серверная оперативная память отличается от обычной?

Следует сразу сказать, что не какой-то особой «серверной» памяти. Есть различные виды оперативной памяти, некоторые из которых подходят для серверов, а некоторые – только для обычных персональных компьютеров.

Основное отличия оперативной памяти для серверов в том, что последняя должна поддерживать технологию ECC (Error Correction Code), кода коррекции ошибок. Эта память способна обнаруживать и исправлять возникающие ошибки данных в битах памяти. Для обычных пользовательских компьютеров распознавание и автоматическая коррекция ошибок некритичны, поскольку нагрузка серверов и обычных компьютеров несравнимы между собой по объёму потоков данных, поэтому битовые сбои в обычных компьютерах происходят гораздо реже, чем в серверах.

Есть и другие отличия серверной памяти, например, буферизованная и не буферизованная память, но эти различия больше относятся к различным видам серверной памяти как таковой.

ECC

Поддержка ЕСС (Error Correction Code) – главная особенность серверной памяти, которая значительно удорожает на 10-30% цену памяти для серверов. Бывают системные администраторы, которые, желая сэкономить деньги компании, ставят в сервер память для обычного десктопа, и сервер при этом иногда работает. Но обычно это случается, во-первых, лишь для серверов начального класса, а во-вторых, возможность сбоев работы сервера значительно возрастает.

ECC даёт возможность исправлять ошибок одиночных битов в оперативной памяти. Если для обычных десктопов такие ошибки не очно критичны, то для серверов, с высокой интенсивностью вычислений, такие ошибки могут приводить к серьёзным сбоям бизнес-процессов и к убыткам предприятий.

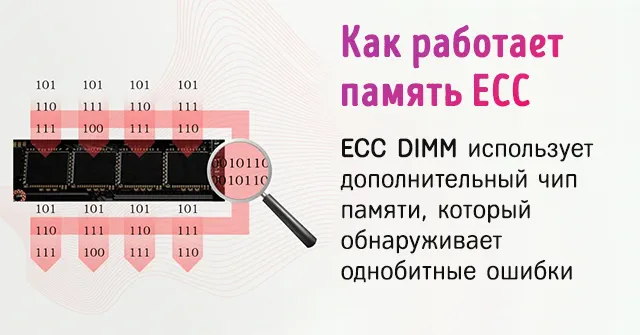

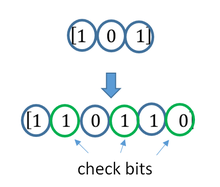

ECC-память содержит специальные контрольные биты и дополнительные контроллеры памяти, которые управляют этими битами в специальной микросхеме модуля памяти. В них хранится код ЕСС, вносимый при записи данных. Во время считывания данных код ECC, созданный при записи корректных данных, сопоставляется с кодом ECC, созданным при чтении данных. Если код, созданный при чтении, не соответствует коду при записи, то при его дешифровке можно определить, какой бит подвергся искажению, после чего этот бит немедленно исправляется.

Рис. 1. Принцип работы ЕСС.

ECC, используется в компьютерах с повышенными требованиями устойчивости к повреждению битов данных, например, для научных или финансовых вычислений, а также в корпоративных серверах.

Некоторые системные платы и процессоры для менее критичных приложений могут не поддерживать использование памяти ЕСС, и их цена может быть ниже. Некоторые системы могут поддерживать не буферизованные модули памяти ECC, но при этом могут также работать и с не-ЕСС памятью. В этом случае, функционал ECC обеспечивается системным встроенным ПО (firmware) и такие системы могут стоить дороже.

Модули памяти с ЕСС предназначены для обеспечения большей стабильности, чем обычные модули памяти. Однако, у них есть и некоторые недостатки.

Во-первых, не каждый компьютер может поддерживать память ECC. Большинство серверов и рабочих станций поддерживает ЕСС, но мало какие обычные пользовательские компьютеры её поддерживают. Либо, они вообще с такой память не будут работать, либо функционал ECC не будет задействован.

Во-вторых, вследствие наличие дополнительного чипа ЕСС, и вообще более сложной структуры памяти ЕСС, она стоит дороже, чем обычная, на 10-30%.

В-третьих, ECC RAM немного медленнее, чем не-ЕСС, однако, ненамного, в среднем на 2-5%.

Рис. 2. Модули память ЕСС и не-ЕСС.

Итак, наличие ЕСС – основное отличие серверной оперативной памяти от обычной. Чтобы понять, чем они ещё отличаются, рассмотрим подробнее, какие вообще бывают виды оперативной памяти ОЗУ, или RAM (Random Access Memory), и какие виды, где используются.

Буферизованная и небуферизованная память

Есть два основных типа оперативной памяти ОЗУ – буферизованная (buffered) и небуферизованная (unbuffered). В буферизованной памяти есть т.н. уровень повышения мощности обработки (processing power), который ускоряет процессы записи и считывания. В такой памяти модули памяти – 4-битовые, в отличие от 8-16 битовых в небуферизованной памяти.

Основное отличие буферизованной памяти – наличие чипа буфера, который обрабатывает информацию, получаемую от процессора (CPU). Буферный чип затем посылает эту информацию в другие чипы модуля ОЗУ. Такая буферизация позволяет централизовать посылку информации из CPU в чипы ОЗУ. Например, популярный модуль ОЗУ PC3-10600 имеет 18 микросхем памяти, поэтому буферизация для взаимодействия с CPU значительно упрощает работу последнего.

При использовании небуферизованной памяти, CPU будет коммуницировать непосредственно с каждым банком памяти, таким образом, CPU будет посылать информацию на каждый чип на каждом модуле ОЗУ. Хотя при этом система получается немного более расширяемой и гибкой, однако, при этом значительно возрастает потребляемая процессором мощность, и это осложняет выполнение других задач.

В серверах используются, в основном, буферизованные ОЗУ.

Различные типы буферизованной памяти

Регистровая память (Registered Memory, RDIMM, DIMM – Dual In-line Memory Module) – имеет дополнительный чип, который выполняет промежуточные операции между CPU и чипами модулей ОЗУ. Он уменьшает количество сигналов, передаваемых между ОЗУ и CPU. Регистровая память RDIMM, в отличие от небуферизованной UDIMM (Inbuffered DIMM), снижает электрическую нагрузку на компоненты системы, однако, немного снижает производительность. Однако, при этом система может иметь более широкое адресное пространство, чем в небуферизованной памяти. Почти все типы регистровой памяти поддерживают код коррекцию ошибок ECC. Регистровую и небуферизованную память нельзя совмещать в одной системе, даже если она поддерживает оба типа.

Полностью буферизованная память (Fully Buffered Memory, FBDIMM) – это более старая версия регистровой памяти. В DDR3 такая память не используется. Полностью буферизованная память DDR2 и небуферизованная память DDR2 имели различные типоразмеры, чтобы не спутать их при установке.

Память со сниженной нагрузкой (Load Reduced Memory, LRDIMM) – более новая версия буферизованной памяти, где используется чип буфера, ещё более снижающий электрическую нагрузку. При этом снижаются или даже полностью устраняются проблемы с рангами памяти (о чем ниже), что позволяет использовать модули памяти высокой ёмкости без снижения производительности системы (или по крайней мере, снизить этот эффект). Кроме того, LRDIMM даёт возможность не стараться обязательно заполнить все гнёзда на системной плате модулями памяти. Однако, LRDIMM, также как UDIMM и RDIMM, не может сочетаться с другими стандартами в одной системе.

Ранги памяти

Ранг – это число 64-битных областей памяти. Модули памяти могут быть одно-, двух-, четырёх- и восьми-ранговые. Большого влияния на обычные компьютеры это разделение не имеет, однако, для регистровой памяти в серверах они приводят к некоторым ограничениям.

Рис. 3. Виды модулей памяти.

Модули с высшими рангами могут иметь ограничения на то, сколько модулей может быть установлено. Например, если в системе – шесть гнёзд для модулей DIMM, то для 4-ранговых модулей можно занимать только 4 гнезда. Можно ли занимать остальные два гнезда, например, 2- или 1-ранговыми модулями DIMM – зависит от параметров системы. Иногда так делать можно, но следует использовать только определённые гнезда для таких целей. Использование модулей высоких рангов иногда приводит к снижению производительности системы. Таким образом, использование того или иного ранга модулей – часто бывает вопросом компромисса между объёмом ОЗУ и производительностью системы. С одной стороны – чем выше ёмкость ОЗУ, тем выше производительность, с другой стороны, чем выше ранг (и, следовательно, больше объём ОЗУ) тем производительность может быть ниже.

Конструктивные отличия серверной памяти

Серверная память, в особенности, RDIMM и LRDIMM, может отличаться по типоразмерам от памяти для рабочих компьютеров. Кроме того, что модулях серверной памяти бывает напаяно больше компонентов, там могут ещё устанавливаться и теплоотводы, поскольку при работе памяти в сервер выделяется больше тепла, как процессором, так и памятью. Для серверных модулей памяти может также понадобиться больше пространства над ними, для отведения тепловых потоков. Иногда, это обстоятельство вынуждает приобретать специальные низкопрофильные модули VLP (Very Low Profile). Многие пользователи именно такие модули и стараются приобретать, поскольку они в любом случае обеспечивают лучший теплоотвод.

Выводы

Как видим, память серверов имеет некоторые особенности по сравнению с памятью для обычных компьютеров. Прежде всего, это необходимость использования кодов коррекции ошибок ЕСС. Если использовать для сервера обычную память без ЕСС, то либо такая система не заработает, либо её работа будет связана с рисками сбоев, что в корпоративных ИТ-системах недопустимо.

Кроме того, для серверов обычно используется буферизованная память, которая оснащена дополнительным чипом для выполнения промежуточных операции между CPU и чипами модулей DIMM.

Иногда серверная память может иметь и конструктивные особенности, например, размещаться в низкопрофильных DIMM для лучшего теплоотвода внутри корпуса сервера.

Вы ищете память, которая имеет доступ к более высоким скоростям и совместима с большим количеством платформ? Или вы ищете долговечную память, которая может работать 24 часа в сутки, 7 дней в неделю, выявлять больше ошибок, но для этого приходится жертвовать скоростью?

Модули ОЗУ (оперативной памяти) являются важной частью каждой системы, но не все модули одинаковы. Помимо емкости, частоты и задержки, модули могут характеризоваться наличием или отсутствием системы исправления ошибок (ECC).

Разница между ними заключается в том, что память ECC защитит вашу систему от потенциального сбоя, исправив любые ошибки в данных, в то время как память без ECC игнорирует такие ошибки.

Думайте о памяти без ECC как о памяти, ориентированной на скорость, а ECC – памяти, ориентированной на выносливость и надёжности.

Поскольку не все платформы поддерживают ECC-память, и не каждой системе она нужна, давайте обсудим, что такое ECC-память, как она работает и нужна ли она вам.

Что такое ECC-память

Чтобы понять, как работает память с коррекцией ошибок (ECC), сначала нужно понять, что такое однобитовая ошибка. Потому что это основная проблема, для решения которой была создан ECC.

Однобитовая ошибка – это когда один бит (двоичный 0 или 1) в данных в ОЗУ случайно изменяется на противоположное значение.

Такого рода ошибки незначительны, и компьютер может не распознать их автоматически, что может привести ко многим проблемам.

Вы можете думать об однобитовых ошибках как о метафорических сорняках на лужайке. Ваш газон – это оперативная память, а ECC-часть вашей памяти – это использование гербицида.

Память без ECC не избавит вас от «сорняков». ECC уничтожит все сорняки, но газон будет расти немного медленнее.

Однобитовые ошибки могут возникать из-за магнитных или электрических помех внутри компьютера, присутствующих в каждой системе в виде фонового излучения.

Перенапряжение, колебания температуры, удар по корпусу или даже чтение или запись данных не так, как предполагалось изначально, могут привести к однобитовой ошибке.

Память ECC позаботится об этих ошибках и исправит их до того, как они превратятся в большую проблему.

Память с ECC очень похожа на память без ECC. Самая большая разница между ними заключается в том, что память ECC обычно имеет немного дополнительной памяти, предназначенной исключительно для обеспечения того, чтобы фактическая память работала без ошибок.

ECC – это, по сути, небольшой чип на обычной планке ОЗУ, который гарантирует, что каждый бит данных, который входит и выходит, является именно тем, чем он должен быть.

Что он делает, так это то, что создаёт зашифрованный фрагмент кода из данных, записываемых в основную память, и сохраняет этот код в дополнительном бите памяти. Когда необходимо получить доступ к данным, хранящимся в основной памяти, он создаёт новый код и сравнивает этот фрагмент кода с кодом, который был сгенерирован ранее.

Если он обнаружит, что они оба одинаковы и что данные не были каким-либо образом изменены, он разрешает чтение данных. Но, если он обнаруживает, что новый код отличается от сохраненного кода, он попытается решить проблему, расшифровывая код, чтобы точно определить, в чём заключается ошибка.

Если он не сможет найти ошибку, то, по крайней мере, гарантирует, что вы будете знать, что что-то пошло не так, вместо того, чтобы молча продолжать работать.

Это похоже на сравнение хэшей MD5 при загрузке программы, чтобы убедиться, что вы загружаете именно то, что вам действительно нужно, а не другой мошеннический секретный файл.

Вот почему ECC работает немного медленнее – потому что ему приходится создавать эти дополнительные коды.

Согласно исследованиям, вероятность возникновения такой ошибки составляет одна однобитовая ошибка каждые 14-40 часов на гигабит ОЗУ.

Необходимость исправления ошибок на серверах и рабочих станциях

В системе, используемой для повседневного просмотра и игр, исправление ошибок не является необходимостью. Однако, в мире серверов и профессиональных рабочих станций ставки выше.

Если вы ведёте бизнес, специализирующийся на финансах, однобитовая ошибка может привести к сбою сервера, который потенциально может стереть транзакции с вашего сервера.

Такая ошибка памяти также может привести к ошибке транскрипции данных, что может привести к неправильному размещению десятичного разделителя или изменению числа.

Очевидно, что это наносит ущерб честности и надёжности бизнеса. Если бы вы пошли покупать кошке новую игрушку и в итоге заплатили 1000 рублей вместо 100, это было бы довольно трагично.

Если вы посетили своего врача, и счет составил 56 987 рублей вместо 5945 рублей, вы только что стали жертвой компьютерной ошибки, связанной с ECC. И вы, скорее всего, больше никогда не воспользуетесь их услугами.

Потеря времени – ещё одна проблема, которую может предотвратить память ECC. Если вы визуализируете сложные изображения в высоком разрешении или работаете с моделью глубокого обучения, необходимость начинать заново после нескольких недель обработки из-за некоторых ошибок памяти – это огромная трата времени и денег для вашего бизнеса.

Память ECC необходима и в медицинской промышленности. При уходе за пациентом точность записей имеет решающее значение, и ошибка в одном бите может привести к неправильному диагнозу, что может привести к летальному исходу.

Выбор памяти может создать или уничтожить репутацию бизнеса.

Без памяти ECC не только существует вероятность подобных ошибок, но вы также не узнаете, что они произошли, пока кто-нибудь не просмотрит данные и не найдёт ошибку. А иногда это может быть слишком поздно.

Какие платформы поддерживают память ECC

Что касается серверов, то линейки процессоров Intel Xeon и линейки серверов AMD Epyc поддерживают память ECC. Обратите внимание, что для использования памяти ECC и процессор, и используемая материнская плата должны поддерживать память ECC.

Помните аналогию с газоном и гербицидом? Думайте о процессоре и материнской плате как об инструментах, которые вы используете для эффективной работы с ECC. Вам нужны подходящие инструменты для распространения гербицидов на газоне.

На основных платформах, используемых сегодня, большинство процессоров Intel (даже некоторые бюджетные модели Celeron) будут поддерживать память ECC, если вы используете материнскую плату, совместимую с такой памятью.

С AMD все процессоры Ryzen поддерживают память ECC с совместимой материнской платой с набором микросхем X570, тогда как набор микросхем B550 не поддерживает память ECC с процессорами Ryzen 2000. Процессоры Ryzen со встроенной видеокартой или ускоренным процессором (APU), серии 3000 G и серии 4000 G потребуют от вас использования процессора PRO для поддержки ECC.

Недостатки использования памяти ECC

Наиболее распространенная проблема с памятью ECC – совместимость. Несмотря на то, что большинство современных платформ поддерживают её, вы должны убедиться, что конкретная комбинация процессора и материнской платы работает с памятью ECC.

Это менее проблематично в мире серверов, где обычно используется память ECC. Серверное оборудование обычно поддерживает ECC по умолчанию.

Ценник тоже отличается. Модули памяти с ECC дороже, чем модули без ECC из-за дополнительных функций. В зависимости от емкости, которую вы покупаете, разница в цене составляет около 10-20%.

Также наблюдается небольшой спад производительности из-за дополнительного времени, которое требуется памяти ECC для проверки наличия ошибок. По словам Corsair, можно ожидать падения около 2%.

Подведение итогов – нужна ли вам память ECC

Когда вы создаете профессиональную рабочую станцию или сервер, который должен работать круглосуточно и без выходных, память ECC просто необходима.

Обойтись без ECC в этом сценарии было бы все равно, что использовать борзую, чтобы тянуть повозку, когда вам нужна крепкая рабочая лошадка.

И разница в цене, и снижение производительности того стоят, если учесть, что вам не придётся беспокоиться о возможности однобитовой ошибки, которая вызовет у вас головную боль.

Вы ведь не хотели бы перепроверять каждую квитанцию, чтобы убедиться, что она верна, верно? Проявите такую же любезность к своим клиентам и заказчикам.

Но если всё, что вы делаете, это играете в игры и используете свой компьютер для другой некритической работы, вам, скорее всего, не понадобится ECC, и вам важнее сохранить эти 2% производительности.

В продолжение рубрики «конспект админа» хотелось бы разобраться в нюансах технологий ОЗУ современного железа: в регистровой памяти, рангах, банках памяти и прочем. Подробнее коснемся надежности хранения данных в памяти и тех технологий, которые несчетное число раз на дню избавляют администраторов от печалей BSOD.

Старые песни про новые типы

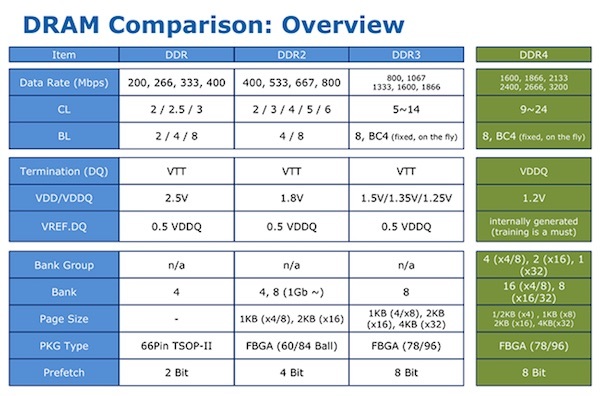

Сегодня на рынке представлены, в основном, модули с памятью DDR SDRAM: DDR2, DDR3, DDR4. Разные поколения отличаются между собой рядом характеристик — в целом, каждое следующее поколение «быстрее, выше, сильнее», а для любознательных вот табличка:

Для подбора правильной памяти больший интерес представляют сами модули:

-

RDIMM — регистровая (буферизованная) память. Удобна для установки большого объема оперативной памяти по сравнению с небуферизованными модулями. Из минусов — более низкая производительность;

-

UDIMM (unregistered DRAM) — нерегистровая или небуферизованная память — это оперативная память, которая не содержит никаких буферов или регистров;

-

LRDIMM — эти модули обеспечивают более высокие скорости при большей емкости по сравнению с двухранговыми или четырехранговыми модулями RDIMM, за счёт использования дополнительных микросхем буфера памяти;

-

HDIMM (HyperCloud DIMM, HCDIMM) — модули с виртуальными рангами, которые имеют большую плотность и обеспечивают более высокую скорость работы. Например, 4 физических ранга в таких модулях могут быть представлены для контроллера как 2 виртуальных;

-

FBDIMM — полностью буферизованная DIMM с высокой надежностью, скоростью и плотностью размещения.

Попытка одновременно использовать эти типы может вызвать самые разные печальные последствия, вплоть до порчи материнской платы или самой памяти. Но возможно использование одного типа модулей с разными характеристиками, так как они обратно совместимы по тактовой частоте. Правда, итоговая частота работы подсистемы памяти будет ограничена возможностями самого медленного модуля или контроллера памяти.

Для всех типов памяти SDRAM есть общий набор базовых характеристик, влияющий на объем и производительность:

-

частота и режим работы;

-

ранг;

-

тайминги.

Конечно, отличий на самом деле больше, но для сборки правильно работающей системы можно ограничиться этими.

Частота и режим работы

Понятно, что чем выше частота — тем выше общая производительность памяти. Но память все равно не будет работать быстрее, чем ей позволяет контроллер на материнской плате. Кроме того, все современные модули умеют работать в в многоканальном режиме, который увеличивает общую производительность до четырех раз.

Режимы работы можно условно разделить на четыре группы:

-

Single Mode — одноканальный или ассиметричный. Включается, когда в системе установлен только один модуль памяти или все модули отличаются друг от друга. Фактически, означает отсутствие многоканального доступа;

-

Dual Mode — двухканальный или симметричный. Слоты памяти группируются по каналам, в каждом из которых устанавливается одинаковый объем памяти. Это позволяет увеличить скорость работы на 5-10% в играх, и до 70% в тяжелых графических приложениях. Модули памяти необходимо устанавливать парами на разные каналы. Производители материнских плат обычно выделяют парные слоты одним цветом;

-

Triple Mode — трехканальный режим работы. Модули устанавливаются группами по три штуки — на каждый из трех каналов. Аналогично работают и последующие режимы: четырехканальные (quad-channel), восьмиканальные (8-channel memory) и т.п.

-

Flex Mode — позволяет увеличить производительность оперативной памяти при установке двух модулей различного объема, но с одинаковой частотой.

-

Для максимального быстродействия лучше устанавливать одинаковые модули с максимально возможной для системы частотой. При этом используйте установку парами или группами — в зависимости от доступного многоканального режима работы.

Ранги для памяти

Ранг (rank) — область памяти из нескольких чипов памяти в 64 бита (72 бита при наличии ECC, о чем поговорим позже). В зависимости от конструкции модуль может содержать один, два или четыре ранга.

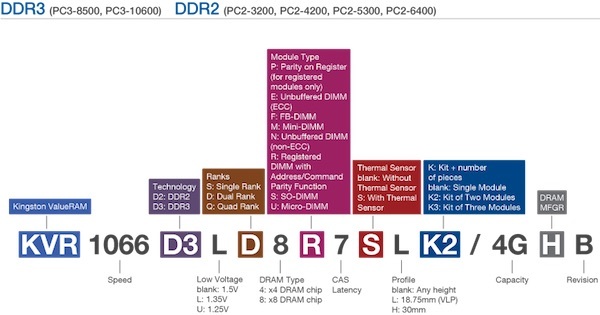

Узнать этот параметр можно из маркировки на модуле памяти. Например уKingston число рангов легко вычислить по одной из трех букв в середине маркировки: S (Single — одногоранговая), D (Dual — двухранговая), Q (Quad — четырехранговая).

Пример полной расшифровки маркировки на модулях Kingston:

Серверные материнские платы ограничены суммарным числом рангов памяти, с которыми могут работать. Например, если максимально может быть установлено восемь рангов при уже установленных четырех двухранговых модулях, то в свободные слоты память добавить не получится.

Перед покупкой модулей есть смысл уточнить, какие типы памяти поддерживает процессор сервера. Например, Xeon E5/E5 v2 поддерживают одно-, двух- и четырехранговые регистровые модули DIMM (RDIMM), LRDIMM и не буферизированные ECC DIMM (ECC UDIMM) DDR3. А процессоры Xeon E5 v3 поддерживают одно- и двухранговые регистровые модули DIMM, а также LRDIMM DDR4.

Немного про скучные аббревиатуры таймингов

Тайминги или латентность памяти (CAS Latency, CL) — величина задержки в тактах от поступления команды до ее исполнения. Числа таймингов указывают параметры следующих операций:

-

CL (CAS Latency) — время, которое проходит между запросом процессора некоторых данных из памяти и моментом выдачи этих данных памятью;

-

tRCD (задержка от RAS до CAS) — время, которое должно пройти с момента обращения к строке матрицы (RAS) до обращения к столбцу матрицы (CAS) с нужными данными;

-

tRP (RAS Precharge) — интервал от закрытия доступа к одной строке матрицы, и до начала доступа к другой;

-

tRAS — пауза для возврата памяти в состояние ожидания следующего запроса;

-

CMD (Command Rate) — время от активации чипа памяти до обращения к ней с первой командой.

Разумеется, чем меньше тайминги — тем лучше для скорости. Но за низкую латентность придется заплатить тактовой частотой: чем ниже тайминги, тем меньше допустимая для памяти тактовая частота. Поэтому правильным выбором будет «золотая середина».

Существуют и специальные более дорогие модули с пометкой «Low Latency», которые могут работать на более высокой частоте при низких таймингах. При расширении памяти желательно подбирать модули с таймингами, аналогичными уже установленным.

RAID для оперативной памяти

Ошибки при хранении данных в оперативной памяти неизбежны. Они классифицируются как аппаратные отказы и нерегулярные ошибки (сбои). Память с контролем четности способна обнаружить ошибку, но не способна ее исправить.

Для коррекции нерегулярных ошибок применяется ECC-память, которая содержит дополнительную микросхему для обнаружения и исправления ошибок в отдельных битах.

Метод коррекции ошибок работает следующим образом:

-

При записи 64 бит данных в ячейку памяти происходит подсчет контрольной суммы, составляющей 8 бит.

-

Когда процессор считывает данные, то выполняется расчет контрольной суммы полученных данных и сравнение с исходным значением. Если суммы не совпадают — это ошибка.

-

Если ошибка однобитовая, то неправильный бит исправляется автоматически. Если двухбитовая — передается соответствующее сообщение для операционной системы.

Технология Advanced ECC способна исправлять многобитовые ошибки в одной микросхеме, и с ней возможно восстановление данных даже при отказе всего модуля DRAM.

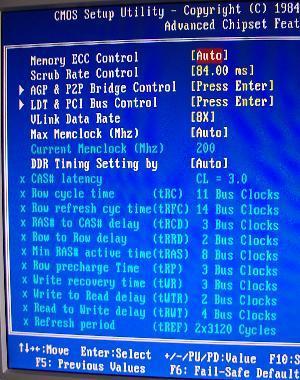

Исправление ошибок нужно отдельно включить в BIOS

Большинство серверных модулей памяти являются регистровыми (буферизованными) — они содержат регистры контроля передачи данных.

Регистры также позволяют устанавливать большие объемы памяти, но из-за них образуются дополнительные задержки в работе. Дело в том, что каждое чтение и запись буферизуются в регистре на один такт, прежде чем попадут с шины памяти в чип DRAM, поэтому регистровая память оказывается медленнее не регистровой на один такт.

Источник — nix.ru

Все регистровые модули и память с полной буферизацией также поддерживают ECC, а вот обратное не всегда справедливо. Из соображений надежности для сервера лучше использовать регистровую память.

Многопроцессорные системы и память

Для правильной и быстрой работы нескольких процессоров, нужно каждому из них выделить свой банк памяти для доступа «напрямую». Об организации этих банков в конкретном сервере лучше почитать в документации, но общее правило такое: память распределяем между банками поровну и в каждый ставим модули одного типа.

Если пришлось поставить в сервер модули с меньшей частотой, чем требуется материнской плате — нужно включить в BIOS дополнительные циклы ожидания при работе процессора с памятью.

Для автоматического учета всех правил и рекомендаций по установке модулей можно использовать специальные утилиты от вендора. Например, у HP есть Online DDR4 (DDR3) Memory Configuration Tool.

Итого

Вместо пространственного заключения приведу общие рекомендации по выбору памяти:

-

Для многопроцессорных серверов HP рекомендуется использовать только регистровую память c функцией коррекции ошибок (ECC RDIMM), а для однопроцессорных — небуферизированную с ECC (UDIMM). Планки UDIMM для серверов HP лучше выбирать от этого же производителя, чтобы избежать самопроизвольных перезагрузок.

-

В случае с RDIMM лучше выбирать одно- и двухранговые модули (1rx4, 2rx4). Для оптимальной производительности используйте двухранговые модули памяти в конфигурациях 1 или 2 DIMM на канал. Создание конфигурации из 3 DIMM с установкой модулей в третий банк памяти значительно снижает производительность.

-

Из тех же соображений максимальной скорости желательно избегать использования четырехранговой памяти RDIMM, поскольку она снижает частоту до 1066 МГц в конфигурациях с одним модулем на канал, и до 800 МГц — в конфигурациях с двумя модулями на канал. Справедливо для серверов на базе Intel Xeon 5600 и Xeon E5/E5 v2.

Список короткий, но здесь все самое необходимое и наименее очевидное. Конечно же, старый как мир принцип RTFM никто не отменял.

ECC, от английского error-correcting code, переводиться на русский язык, как код коррекции ошибок. Встроенная в контроллёры флешек технология, обнаружения и исправления ошибок при передаче данных. ECC способна справиться только с несущественными проблемами, в тяжелых случаях флешка заблокируется на запись данных.

ЗАЧЕМ ЭТО НАДО

Если в эпоху качественных SLC и MLC микросхем флэш-памяти, не было особого смысла обращать внимание на этот механизм исправления ошибок. То сейчас когда в подавляющем количестве флешек, установлена или банально TLC-память или какая-нибудь MLC DownGrade, не стоит пренебрегать настройками ECC-механизма.

Данная технология позволяет продлить жизнь флешки до следующих затыков с ней, ведь не хочется, каждый месяц заново перепрошивать свою флешку.

Еще одной положительной чертой, является вероятность достижения максимального возможного объёма флэш-диска. Он может быть даже выше, чем изначально имел носитель, особенно у флешек с отбракованными микросхемами.

НЕДОСТАТКИ

Чем выше вы установите значение ECC-параметра, тем большую нагрузку он создаст на контроллёр флешки. А это в свою очередь, может негативно сказаться на её производительность, т.е. скорость работы. Также из заметных недостатков, высокой нагрузки, это больший разогрев флешки.

РЕКОМЕНДУЕМЫЕ ЗНАЧЕНИЯ ПАРАМЕТРА ECC

В большинстве утилитах, используется не применяемые в флэш-листах значения (например: 7b/512B и 72b/1K), а суммы определенных параметров. Как правило, в диапазоне равеном от 0 до 15, в некоторых производственных программах, ввиду поддержки крайне некачественной памяти, от 0 до 20. Для посетителей проекта USBDev.ru, я составил следующую таблицу.

| ECC Value | |

|---|---|

| MEMORY TYPE: | ECC: |

| SLC | 1 |

| MLC 32nm, 35nm, 42nm, 50nm, … | 3-4 |

| MLC 24nm, 25nm, 26nm, 32nm | 4-8 |

| MLC 21nm, 20nm, 19nm, … | 8-12 |

| TLC 27nm, 32nm, 43nm, … | 8 |

| TLC 24nm, 21nm, 19nm, … | 12-15 |

В некоторых утилитах, используется другая система координат, к примеру производственный комплекс Dyna для контроллёров SMI. На этот случай, чуть ниже можно обнаружить ссылку на особености настроек у конкретных производителей.

Немного поясню, как следует использовать таблицу данную выше. Так вот, если ваша флешка добротная (хорошо зарекомендовавший себя бренд), то выбирайте минимальное значение из неё. Для подарочных и поддельных флешек, настоятельно советую использовать максимальное значение параметра ECC, для своего типа памяти.

РЕАЛИЗАЦИЯ В ПРОИЗВОДСТВЕННЫХ УТИЛИТАХ

Далеко не во всех утилит, имеется возможность ручной корректировки ECC-опции. Можно сказать что ECC, это такая фитча Sorting-составляющей производственных утилит. Попробую кратко выразить это в таблице, для основных производителей USB-контроллёров.

| ECC Compatible Software | |

|---|---|

| Company: | Tools: |

| ALCOR | AlcorMP_UFD FC MpTool AAMP |

| CHIPSBANK | Chipsbank UMPTool CBM2093 UMPTool CBM2098 UMPTool umptool209X V68 Building Tools |

| INNOSTOR | Innostor MPTool Innostor 917 LFA MP Tool |

| PHISON | UPTool UP19_CTool UP21_CTool UP23_CTool |

| SILICON GO | KingStore Manufacture Tool SiliconGo MPTools SiliconGo MPTool2 |

| SKYMEDI | SK6221 MPTool |

| SMI | Dyna Mass Storage Production Tool |

| СТАТЬИ НА ТЕМУ ECC-КОРРЕКЦИИ | ||

|---|---|---|

| ECC значения для контроллёров Alcor с DownGrade памятью | 2015 | |

| Настройка ECC у контроллёров Silicon Motion (SMI) | 2015 | |

Для ваших вопросов, на проекте USBDev существует форум – FORUM.

«Interleaver» redirects here. For the fiber-optic device, see optical interleaver.

In computing, telecommunication, information theory, and coding theory, an error correction code, sometimes error correcting code, (ECC) is used for controlling errors in data over unreliable or noisy communication channels.[1][2] The central idea is the sender encodes the message with redundant information in the form of an ECC. The redundancy allows the receiver to detect a limited number of errors that may occur anywhere in the message, and often to correct these errors without retransmission. The American mathematician Richard Hamming pioneered this field in the 1940s and invented the first error-correcting code in 1950: the Hamming (7,4) code.[2]

ECC contrasts with error detection in that errors that are encountered can be corrected, not simply detected. The advantage is that a system using ECC does not require a reverse channel to request retransmission of data when an error occurs. The downside is that there is a fixed overhead that is added to the message, thereby requiring a higher forward-channel bandwidth. ECC is therefore applied in situations where retransmissions are costly or impossible, such as one-way communication links and when transmitting to multiple receivers in multicast. Long-latency connections also benefit; in the case of a satellite orbiting around Uranus, retransmission due to errors can create a delay of five hours. ECC information is usually added to mass storage devices to enable recovery of corrupted data, is widely used in modems, and is used on systems where the primary memory is ECC memory.

ECC processing in a receiver may be applied to a digital bitstream or in the demodulation of a digitally modulated carrier. For the latter, ECC is an integral part of the initial analog-to-digital conversion in the receiver. The Viterbi decoder implements a soft-decision algorithm to demodulate digital data from an analog signal corrupted by noise. Many ECC encoders/decoders can also generate a bit-error rate (BER) signal, which can be used as feedback to fine-tune the analog receiving electronics.

The maximum fractions of errors or of missing bits that can be corrected are determined by the design of the ECC code, so different error correcting codes are suitable for different conditions. In general, a stronger code induces more redundancy that needs to be transmitted using the available bandwidth, which reduces the effective bit-rate while improving the received effective signal-to-noise ratio. The noisy-channel coding theorem of Claude Shannon can be used to compute the maximum achievable communication bandwidth for a given maximum acceptable error probability. This establishes bounds on the theoretical maximum information transfer rate of a channel with some given base noise level. However, the proof is not constructive, and hence gives no insight of how to build a capacity achieving code. After years of research, some advanced ECC systems as of 2016[3] come very close to the theoretical maximum.

Forward error correction[edit]

In telecommunication, information theory, and coding theory, forward error correction (FEC) or channel coding[4][3] is a technique used for controlling errors in data transmission over unreliable or noisy communication channels. The central idea is that the sender encodes the message in a redundant way, most often by using an ECC.

The redundancy allows the receiver to detect a limited number of errors that may occur anywhere in the message, and often to correct these errors without re-transmission. FEC gives the receiver the ability to correct errors without needing a reverse channel to request re-transmission of data, but at the cost of a fixed, higher forward channel bandwidth. FEC is therefore applied in situations where re-transmissions are costly or impossible, such as one-way communication links and when transmitting to multiple receivers in multicast. FEC information is usually added to mass storage (magnetic, optical and solid state/flash based) devices to enable recovery of corrupted data, is widely used in modems, is used on systems where the primary memory is ECC memory and in broadcast situations, where the receiver does not have capabilities to request re-transmission or doing so would induce significant latency. For example, in the case of a satellite orbiting Uranus, a re-transmission because of decoding errors would create a delay of at least 5 hours.

FEC processing in a receiver may be applied to a digital bit stream or in the demodulation of a digitally modulated carrier. For the latter, FEC is an integral part of the initial analog-to-digital conversion in the receiver. The Viterbi decoder implements a soft-decision algorithm to demodulate digital data from an analog signal corrupted by noise. Many FEC coders can also generate a bit-error rate (BER) signal which can be used as feedback to fine-tune the analog receiving electronics.

The maximum proportion of errors or missing bits that can be corrected is determined by the design of the ECC, so different forward error correcting codes are suitable for different conditions. In general, a stronger code induces more redundancy that needs to be transmitted using the available bandwidth, which reduces the effective bit-rate while improving the received effective signal-to-noise ratio. The noisy-channel coding theorem of Claude Shannon answers the question of how much bandwidth is left for data communication while using the most efficient code that turns the decoding error probability to zero. This establishes bounds on the theoretical maximum information transfer rate of a channel with some given base noise level. His proof is not constructive, and hence gives no insight of how to build a capacity achieving code. However, after years of research, some advanced FEC systems like polar code[3] achieve the Shannon channel capacity under the hypothesis of an infinite length frame.

How it works[edit]

ECC is accomplished by adding redundancy to the transmitted information using an algorithm. A redundant bit may be a complex function of many original information bits. The original information may or may not appear literally in the encoded output; codes that include the unmodified input in the output are systematic, while those that do not are non-systematic.

A simplistic example of ECC is to transmit each data bit 3 times, which is known as a (3,1) repetition code. Through a noisy channel, a receiver might see 8 versions of the output, see table below.

| Triplet received | Interpreted as |

|---|---|

| 000 | 0 (error-free) |

| 001 | 0 |

| 010 | 0 |

| 100 | 0 |

| 111 | 1 (error-free) |

| 110 | 1 |

| 101 | 1 |

| 011 | 1 |

This allows an error in any one of the three samples to be corrected by «majority vote», or «democratic voting». The correcting ability of this ECC is:

- Up to 1 bit of triplet in error, or

- up to 2 bits of triplet omitted (cases not shown in table).

Though simple to implement and widely used, this triple modular redundancy is a relatively inefficient ECC. Better ECC codes typically examine the last several tens or even the last several hundreds of previously received bits to determine how to decode the current small handful of bits (typically in groups of 2 to 8 bits).

Averaging noise to reduce errors[edit]

ECC could be said to work by «averaging noise»; since each data bit affects many transmitted symbols, the corruption of some symbols by noise usually allows the original user data to be extracted from the other, uncorrupted received symbols that also depend on the same user data.

- Because of this «risk-pooling» effect, digital communication systems that use ECC tend to work well above a certain minimum signal-to-noise ratio and not at all below it.

- This all-or-nothing tendency – the cliff effect – becomes more pronounced as stronger codes are used that more closely approach the theoretical Shannon limit.

- Interleaving ECC coded data can reduce the all or nothing properties of transmitted ECC codes when the channel errors tend to occur in bursts. However, this method has limits; it is best used on narrowband data.

Most telecommunication systems use a fixed channel code designed to tolerate the expected worst-case bit error rate, and then fail to work at all if the bit error rate is ever worse.

However, some systems adapt to the given channel error conditions: some instances of hybrid automatic repeat-request use a fixed ECC method as long as the ECC can handle the error rate, then switch to ARQ when the error rate gets too high;

adaptive modulation and coding uses a variety of ECC rates, adding more error-correction bits per packet when there are higher error rates in the channel, or taking them out when they are not needed.

Types of ECC[edit]

A block code (specifically a Hamming code) where redundant bits are added as a block to the end of the initial message

A continuous code convolutional code where redundant bits are added continuously into the structure of the code word

The two main categories of ECC codes are block codes and convolutional codes.

- Block codes work on fixed-size blocks (packets) of bits or symbols of predetermined size. Practical block codes can generally be hard-decoded in polynomial time to their block length.

- Convolutional codes work on bit or symbol streams of arbitrary length. They are most often soft decoded with the Viterbi algorithm, though other algorithms are sometimes used. Viterbi decoding allows asymptotically optimal decoding efficiency with increasing constraint length of the convolutional code, but at the expense of exponentially increasing complexity. A convolutional code that is terminated is also a ‘block code’ in that it encodes a block of input data, but the block size of a convolutional code is generally arbitrary, while block codes have a fixed size dictated by their algebraic characteristics. Types of termination for convolutional codes include «tail-biting» and «bit-flushing».

There are many types of block codes; Reed–Solomon coding is noteworthy for its widespread use in compact discs, DVDs, and hard disk drives. Other examples of classical block codes include Golay, BCH, Multidimensional parity, and Hamming codes.

Hamming ECC is commonly used to correct NAND flash memory errors.[5]

This provides single-bit error correction and 2-bit error detection.

Hamming codes are only suitable for more reliable single-level cell (SLC) NAND.

Denser multi-level cell (MLC) NAND may use multi-bit correcting ECC such as BCH or Reed–Solomon.[6][7] NOR Flash typically does not use any error correction.[6]

Classical block codes are usually decoded using hard-decision algorithms,[8] which means that for every input and output signal a hard decision is made whether it corresponds to a one or a zero bit. In contrast, convolutional codes are typically decoded using soft-decision algorithms like the Viterbi, MAP or BCJR algorithms, which process (discretized) analog signals, and which allow for much higher error-correction performance than hard-decision decoding.

Nearly all classical block codes apply the algebraic properties of finite fields. Hence classical block codes are often referred to as algebraic codes.

In contrast to classical block codes that often specify an error-detecting or error-correcting ability, many modern block codes such as LDPC codes lack such guarantees. Instead, modern codes are evaluated in terms of their bit error rates.

Most forward error correction codes correct only bit-flips, but not bit-insertions or bit-deletions.

In this setting, the Hamming distance is the appropriate way to measure the bit error rate.

A few forward error correction codes are designed to correct bit-insertions and bit-deletions, such as Marker Codes and Watermark Codes.

The Levenshtein distance is a more appropriate way to measure the bit error rate when using such codes.

[9]

Code-rate and the tradeoff between reliability and data rate[edit]

The fundamental principle of ECC is to add redundant bits in order to help the decoder to find out the true message that was encoded by the transmitter. The code-rate of a given ECC system is defined as the ratio between the number of information bits and the total number of bits (i.e., information plus redundancy bits) in a given communication package. The code-rate is hence a real number. A low code-rate close to zero implies a strong code that uses many redundant bits to achieve a good performance, while a large code-rate close to 1 implies a weak code.

The redundant bits that protect the information have to be transferred using the same communication resources that they are trying to protect. This causes a fundamental tradeoff between reliability and data rate.[10] In one extreme, a strong code (with low code-rate) can induce an important increase in the receiver SNR (signal-to-noise-ratio) decreasing the bit error rate, at the cost of reducing the effective data rate. On the other extreme, not using any ECC (i.e., a code-rate equal to 1) uses the full channel for information transfer purposes, at the cost of leaving the bits without any additional protection.

One interesting question is the following: how efficient in terms of information transfer can an ECC be that has a negligible decoding error rate? This question was answered by Claude Shannon with his second theorem, which says that the channel capacity is the maximum bit rate achievable by any ECC whose error rate tends to zero:[11] His proof relies on Gaussian random coding, which is not suitable to real-world applications. The upper bound given by Shannon’s work inspired a long journey in designing ECCs that can come close to the ultimate performance boundary. Various codes today can attain almost the Shannon limit. However, capacity achieving ECCs are usually extremely complex to implement.

The most popular ECCs have a trade-off between performance and computational complexity. Usually, their parameters give a range of possible code rates, which can be optimized depending on the scenario. Usually, this optimization is done in order to achieve a low decoding error probability while minimizing the impact to the data rate. Another criterion for optimizing the code rate is to balance low error rate and retransmissions number in order to the energy cost of the communication.[12]

Concatenated ECC codes for improved performance[edit]

Classical (algebraic) block codes and convolutional codes are frequently combined in concatenated coding schemes in which a short constraint-length Viterbi-decoded convolutional code does most of the work and a block code (usually Reed–Solomon) with larger symbol size and block length «mops up» any errors made by the convolutional decoder. Single pass decoding with this family of error correction codes can yield very low error rates, but for long range transmission conditions (like deep space) iterative decoding is recommended.

Concatenated codes have been standard practice in satellite and deep space communications since Voyager 2 first used the technique in its 1986 encounter with Uranus. The Galileo craft used iterative concatenated codes to compensate for the very high error rate conditions caused by having a failed antenna.

Low-density parity-check (LDPC)[edit]

Low-density parity-check (LDPC) codes are a class of highly efficient linear block

codes made from many single parity check (SPC) codes. They can provide performance very close to the channel capacity (the theoretical maximum) using an iterated soft-decision decoding approach, at linear time complexity in terms of their block length. Practical implementations rely heavily on decoding the constituent SPC codes in parallel.

LDPC codes were first introduced by Robert G. Gallager in his PhD thesis in 1960,

but due to the computational effort in implementing encoder and decoder and the introduction of Reed–Solomon codes,

they were mostly ignored until the 1990s.

LDPC codes are now used in many recent high-speed communication standards, such as DVB-S2 (Digital Video Broadcasting – Satellite – Second Generation), WiMAX (IEEE 802.16e standard for microwave communications), High-Speed Wireless LAN (IEEE 802.11n),[13] 10GBase-T Ethernet (802.3an) and G.hn/G.9960 (ITU-T Standard for networking over power lines, phone lines and coaxial cable). Other LDPC codes are standardized for wireless communication standards within 3GPP MBMS (see fountain codes).

Turbo codes[edit]

Turbo coding is an iterated soft-decoding scheme that combines two or more relatively simple convolutional codes and an interleaver to produce a block code that can perform to within a fraction of a decibel of the Shannon limit. Predating LDPC codes in terms of practical application, they now provide similar performance.

One of the earliest commercial applications of turbo coding was the CDMA2000 1x (TIA IS-2000) digital cellular technology developed by Qualcomm and sold by Verizon Wireless, Sprint, and other carriers. It is also used for the evolution of CDMA2000 1x specifically for Internet access, 1xEV-DO (TIA IS-856). Like 1x, EV-DO was developed by Qualcomm, and is sold by Verizon Wireless, Sprint, and other carriers (Verizon’s marketing name for 1xEV-DO is Broadband Access, Sprint’s consumer and business marketing names for 1xEV-DO are Power Vision and Mobile Broadband, respectively).

Local decoding and testing of codes[edit]

Sometimes it is only necessary to decode single bits of the message, or to check whether a given signal is a codeword, and do so without looking at the entire signal. This can make sense in a streaming setting, where codewords are too large to be classically decoded fast enough and where only a few bits of the message are of interest for now. Also such codes have become an important tool in computational complexity theory, e.g., for the design of probabilistically checkable proofs.

Locally decodable codes are error-correcting codes for which single bits of the message can be probabilistically recovered by only looking at a small (say constant) number of positions of a codeword, even after the codeword has been corrupted at some constant fraction of positions. Locally testable codes are error-correcting codes for which it can be checked probabilistically whether a signal is close to a codeword by only looking at a small number of positions of the signal.

Interleaving[edit]

«Interleaver» redirects here. For the fiber-optic device, see optical interleaver.

A short illustration of interleaving idea

Interleaving is frequently used in digital communication and storage systems to improve the performance of forward error correcting codes. Many communication channels are not memoryless: errors typically occur in bursts rather than independently. If the number of errors within a code word exceeds the error-correcting code’s capability, it fails to recover the original code word. Interleaving alleviates this problem by shuffling source symbols across several code words, thereby creating a more uniform distribution of errors.[14] Therefore, interleaving is widely used for burst error-correction.

The analysis of modern iterated codes, like turbo codes and LDPC codes, typically assumes an independent distribution of errors.[15] Systems using LDPC codes therefore typically employ additional interleaving across the symbols within a code word.[16]

For turbo codes, an interleaver is an integral component and its proper design is crucial for good performance.[14][17] The iterative decoding algorithm works best when there are not short cycles in the factor graph that represents the decoder; the interleaver is chosen to avoid short cycles.

Interleaver designs include:

- rectangular (or uniform) interleavers (similar to the method using skip factors described above)

- convolutional interleavers

- random interleavers (where the interleaver is a known random permutation)

- S-random interleaver (where the interleaver is a known random permutation with the constraint that no input symbols within distance S appear within a distance of S in the output).[18]

- a contention-free quadratic permutation polynomial (QPP).[19] An example of use is in the 3GPP Long Term Evolution mobile telecommunication standard.[20]

In multi-carrier communication systems, interleaving across carriers may be employed to provide frequency diversity, e.g., to mitigate frequency-selective fading or narrowband interference.[21]

Example[edit]

Transmission without interleaving:

Error-free message: aaaabbbbccccddddeeeeffffgggg Transmission with a burst error: aaaabbbbccc____deeeeffffgggg

Here, each group of the same letter represents a 4-bit one-bit error-correcting codeword. The codeword cccc is altered in one bit and can be corrected, but the codeword dddd is altered in three bits, so either it cannot be decoded at all or it might be decoded incorrectly.

With interleaving:

Error-free code words: aaaabbbbccccddddeeeeffffgggg Interleaved: abcdefgabcdefgabcdefgabcdefg Transmission with a burst error: abcdefgabcd____bcdefgabcdefg Received code words after deinterleaving: aa_abbbbccccdddde_eef_ffg_gg

In each of the codewords «aaaa», «eeee», «ffff», and «gggg», only one bit is altered, so one-bit error-correcting code will decode everything correctly.

Transmission without interleaving:

Original transmitted sentence: ThisIsAnExampleOfInterleaving Received sentence with a burst error: ThisIs______pleOfInterleaving

The term «AnExample» ends up mostly unintelligible and difficult to correct.

With interleaving:

Transmitted sentence: ThisIsAnExampleOfInterleaving... Error-free transmission: TIEpfeaghsxlIrv.iAaenli.snmOten. Received sentence with a burst error: TIEpfe______Irv.iAaenli.snmOten. Received sentence after deinterleaving: T_isI_AnE_amp_eOfInterle_vin_...

No word is completely lost and the missing letters can be recovered with minimal guesswork.

Disadvantages of interleaving[edit]

Use of interleaving techniques increases total delay. This is because the entire interleaved block must be received before the packets can be decoded.[22] Also interleavers hide the structure of errors; without an interleaver, more advanced decoding algorithms can take advantage of the error structure and achieve more reliable communication than a simpler decoder combined with an interleaver[citation needed]. An example of such an algorithm is based on neural network[23] structures.

Software for error-correcting codes[edit]

Simulating the behaviour of error-correcting codes (ECCs) in software is a common practice to design, validate and improve ECCs. The upcoming wireless 5G standard raises a new range of applications for the software ECCs: the Cloud Radio Access Networks (C-RAN) in a Software-defined radio (SDR) context. The idea is to directly use software ECCs in the communications. For instance in the 5G, the software ECCs could be located in the cloud and the antennas connected to this computing resources: improving this way the flexibility of the communication network and eventually increasing the energy efficiency of the system.

In this context, there are various available Open-source software listed below (non exhaustive).

- AFF3CT(A Fast Forward Error Correction Toolbox): a full communication chain in C++ (many supported codes like Turbo, LDPC, Polar codes, etc.), very fast and specialized on channel coding (can be used as a program for simulations or as a library for the SDR).

- IT++: a C++ library of classes and functions for linear algebra, numerical optimization, signal processing, communications, and statistics.

- OpenAir: implementation (in C) of the 3GPP specifications concerning the Evolved Packet Core Networks.

List of error-correcting codes[edit]

| Distance | Code |

|---|---|

| 2 (single-error detecting) | Parity |

| 3 (single-error correcting) | Triple modular redundancy |

| 3 (single-error correcting) | perfect Hamming such as Hamming(7,4) |

| 4 (SECDED) | Extended Hamming |

| 5 (double-error correcting) | |

| 6 (double-error correct-/triple error detect) | Nordstrom-Robinson code |

| 7 (three-error correcting) | perfect binary Golay code |

| 8 (TECFED) | extended binary Golay code |

- AN codes

- BCH code, which can be designed to correct any arbitrary number of errors per code block.

- Barker code used for radar, telemetry, ultra sound, Wifi, DSSS mobile phone networks, GPS etc.

- Berger code

- Constant-weight code

- Convolutional code

- Expander codes

- Group codes

- Golay codes, of which the Binary Golay code is of practical interest

- Goppa code, used in the McEliece cryptosystem

- Hadamard code

- Hagelbarger code

- Hamming code

- Latin square based code for non-white noise (prevalent for example in broadband over powerlines)

- Lexicographic code

- Linear Network Coding, a type of erasure correcting code across networks instead of point-to-point links

- Long code

- Low-density parity-check code, also known as Gallager code, as the archetype for sparse graph codes

- LT code, which is a near-optimal rateless erasure correcting code (Fountain code)

- m of n codes

- Nordstrom-Robinson code, used in Geometry and Group Theory[24]

- Online code, a near-optimal rateless erasure correcting code

- Polar code (coding theory)

- Raptor code, a near-optimal rateless erasure correcting code

- Reed–Solomon error correction

- Reed–Muller code

- Repeat-accumulate code

- Repetition codes, such as Triple modular redundancy

- Spinal code, a rateless, nonlinear code based on pseudo-random hash functions[25]

- Tornado code, a near-optimal erasure correcting code, and the precursor to Fountain codes

- Turbo code

- Walsh–Hadamard code

- Cyclic redundancy checks (CRCs) can correct 1-bit errors for messages at most

bits long for optimal generator polynomials of degree

, see Mathematics of cyclic redundancy checks#Bitfilters

See also[edit]

- Code rate

- Erasure codes

- Soft-decision decoder

- Burst error-correcting code

- Error detection and correction

- Error-correcting codes with feedback

References[edit]

- ^ Glover, Neal; Dudley, Trent (1990). Practical Error Correction Design For Engineers (Revision 1.1, 2nd ed.). CO, USA: Cirrus Logic. ISBN 0-927239-00-0.

- ^ a b Hamming, Richard Wesley (April 1950). «Error Detecting and Error Correcting Codes». Bell System Technical Journal. USA: AT&T. 29 (2): 147–160. doi:10.1002/j.1538-7305.1950.tb00463.x. S2CID 61141773.

- ^ a b c Maunder, Robert (2016). «Overview of Channel Coding».

- ^ Charles Wang; Dean Sklar; Diana Johnson (Winter 2001–2002). «Forward Error-Correction Coding». Crosslink. The Aerospace Corporation. 3 (1). Archived from the original on 14 March 2012. Retrieved 5 March 2006.

How Forward Error-Correcting Codes Work

- ^ «Hamming codes for NAND flash memory devices» Archived 21 August 2016 at the Wayback Machine. EE Times-Asia. Apparently based on «Micron Technical Note TN-29-08: Hamming Codes for NAND Flash Memory Devices». 2005. Both say: «The Hamming algorithm is an industry-accepted method for error detection and correction in many SLC NAND flash-based applications.»

- ^ a b «What Types of ECC Should Be Used on Flash Memory?» (Application note). Spansion. 2011.

Both Reed–Solomon algorithm and BCH algorithm are common ECC choices for MLC NAND flash. … Hamming based block codes are the most commonly used ECC for SLC…. both Reed–Solomon and BCH are able to handle multiple errors and are widely used on MLC flash.

- ^ Jim Cooke (August 2007). «The Inconvenient Truths of NAND Flash Memory» (PDF). p. 28.

For SLC, a code with a correction threshold of 1 is sufficient. t=4 required … for MLC.

- ^ Baldi, M.; Chiaraluce, F. (2008). «A Simple Scheme for Belief Propagation Decoding of BCH and RS Codes in Multimedia Transmissions». International Journal of Digital Multimedia Broadcasting. 2008: 1–12. doi:10.1155/2008/957846.

- ^ Shah, Gaurav; Molina, Andres; Blaze, Matt (2006). «Keyboards and covert channels». USENIX. Retrieved 20 December 2018.

- ^ Tse, David; Viswanath, Pramod (2005), Fundamentals of Wireless Communication, Cambridge University Press, UK

- ^ Shannon, C. E. (1948). «A mathematical theory of communication» (PDF). Bell System Technical Journal. 27 (3–4): 379–423 & 623–656. doi:10.1002/j.1538-7305.1948.tb01338.x. hdl:11858/00-001M-0000-002C-4314-2.

- ^ Rosas, F.; Brante, G.; Souza, R. D.; Oberli, C. (2014). «Optimizing the code rate for achieving energy-efficient wireless communications». Proceedings of the IEEE Wireless Communications and Networking Conference (WCNC). pp. 775–780. doi:10.1109/WCNC.2014.6952166. ISBN 978-1-4799-3083-8.

- ^ IEEE Standard, section 20.3.11.6 «802.11n-2009» Archived 3 February 2013 at the Wayback Machine, IEEE, 29 October 2009, accessed 21 March 2011.

- ^ a b Vucetic, B.; Yuan, J. (2000). Turbo codes: principles and applications. Springer Verlag. ISBN 978-0-7923-7868-6.

- ^ Luby, Michael; Mitzenmacher, M.; Shokrollahi, A.; Spielman, D.; Stemann, V. (1997). «Practical Loss-Resilient Codes». Proc. 29th Annual Association for Computing Machinery (ACM) Symposium on Theory of Computation.

- ^ «Digital Video Broadcast (DVB); Second generation framing structure, channel coding and modulation systems for Broadcasting, Interactive Services, News Gathering and other satellite broadband applications (DVB-S2)». En 302 307. ETSI (V1.2.1). April 2009.

- ^ Andrews, K. S.; Divsalar, D.; Dolinar, S.; Hamkins, J.; Jones, C. R.; Pollara, F. (November 2007). «The Development of Turbo and LDPC Codes for Deep-Space Applications». Proceedings of the IEEE. 95 (11): 2142–2156. doi:10.1109/JPROC.2007.905132. S2CID 9289140.

- ^ Dolinar, S.; Divsalar, D. (15 August 1995). «Weight Distributions for Turbo Codes Using Random and Nonrandom Permutations». TDA Progress Report. 122: 42–122. Bibcode:1995TDAPR.122…56D. CiteSeerX 10.1.1.105.6640.

- ^ Takeshita, Oscar (2006). «Permutation Polynomial Interleavers: An Algebraic-Geometric Perspective». IEEE Transactions on Information Theory. 53 (6): 2116–2132. arXiv:cs/0601048. Bibcode:2006cs……..1048T. doi:10.1109/TIT.2007.896870. S2CID 660.

- ^ 3GPP TS 36.212, version 8.8.0, page 14

- ^ «Digital Video Broadcast (DVB); Frame structure, channel coding and modulation for a second generation digital terrestrial television broadcasting system (DVB-T2)». En 302 755. ETSI (V1.1.1). September 2009.

- ^ Techie (3 June 2010). «Explaining Interleaving». W3 Techie Blog. Retrieved 3 June 2010.

- ^ Krastanov, Stefan; Jiang, Liang (8 September 2017). «Deep Neural Network Probabilistic Decoder for Stabilizer Codes». Scientific Reports. 7 (1): 11003. arXiv:1705.09334. Bibcode:2017NatSR…711003K. doi:10.1038/s41598-017-11266-1. PMC 5591216. PMID 28887480.

- ^ Nordstrom, A.W.; Robinson, J.P. (1967), «An optimum nonlinear code», Information and Control, 11 (5–6): 613–616, doi:10.1016/S0019-9958(67)90835-2

- ^ Perry, Jonathan; Balakrishnan, Hari; Shah, Devavrat (2011). «Rateless Spinal Codes». Proceedings of the 10th ACM Workshop on Hot Topics in Networks. pp. 1–6. doi:10.1145/2070562.2070568. hdl:1721.1/79676. ISBN 9781450310598.

Further reading[edit]

- MacWilliams, Florence Jessiem; Sloane, Neil James Alexander (2007) [1977]. Written at AT&T Shannon Labs, Florham Park, New Jersey, USA. The Theory of Error-Correcting Codes. North-Holland Mathematical Library. Vol. 16 (digital print of 12th impression, 1st ed.). Amsterdam / London / New York / Tokyo: North-Holland / Elsevier BV. ISBN 978-0-444-85193-2. LCCN 76-41296. (xxii+762+6 pages)

- Clark, Jr., George C.; Cain, J. Bibb (1981). Error-Correction Coding for Digital Communications. New York, USA: Plenum Press. ISBN 0-306-40615-2.

- Arazi, Benjamin (1987). Swetman, Herb (ed.). A Commonsense Approach to the Theory of Error Correcting Codes. MIT Press Series in Computer Systems. Vol. 10 (1 ed.). Cambridge, Massachusetts, USA / London, UK: Massachusetts Institute of Technology. ISBN 0-262-01098-4. LCCN 87-21889. (x+2+208+4 pages)

- Wicker, Stephen B. (1995). Error Control Systems for Digital Communication and Storage. Englewood Cliffs, New Jersey, USA: Prentice-Hall. ISBN 0-13-200809-2.

- Wilson, Stephen G. (1996). Digital Modulation and Coding. Englewood Cliffs, New Jersey, USA: Prentice-Hall. ISBN 0-13-210071-1.

- «Error Correction Code in Single Level Cell NAND Flash memories» 2007-02-16

- «Error Correction Code in NAND Flash memories» 2004-11-29

- Observations on Errors, Corrections, & Trust of Dependent Systems, by James Hamilton, 2012-02-26

- Sphere Packings, Lattices and Groups, By J. H. Conway, Neil James Alexander Sloane, Springer Science & Business Media, 2013-03-09 – Mathematics – 682 pages.

External links[edit]

- Morelos-Zaragoza, Robert (2004). «The Correcting Codes (ECC) Page». Retrieved 5 March 2006.

- lpdec: library for LP decoding and related things (Python)

«Interleaver» redirects here. For the fiber-optic device, see optical interleaver.

In computing, telecommunication, information theory, and coding theory, an error correction code, sometimes error correcting code, (ECC) is used for controlling errors in data over unreliable or noisy communication channels.[1][2] The central idea is the sender encodes the message with redundant information in the form of an ECC. The redundancy allows the receiver to detect a limited number of errors that may occur anywhere in the message, and often to correct these errors without retransmission. The American mathematician Richard Hamming pioneered this field in the 1940s and invented the first error-correcting code in 1950: the Hamming (7,4) code.[2]

ECC contrasts with error detection in that errors that are encountered can be corrected, not simply detected. The advantage is that a system using ECC does not require a reverse channel to request retransmission of data when an error occurs. The downside is that there is a fixed overhead that is added to the message, thereby requiring a higher forward-channel bandwidth. ECC is therefore applied in situations where retransmissions are costly or impossible, such as one-way communication links and when transmitting to multiple receivers in multicast. Long-latency connections also benefit; in the case of a satellite orbiting around Uranus, retransmission due to errors can create a delay of five hours. ECC information is usually added to mass storage devices to enable recovery of corrupted data, is widely used in modems, and is used on systems where the primary memory is ECC memory.

ECC processing in a receiver may be applied to a digital bitstream or in the demodulation of a digitally modulated carrier. For the latter, ECC is an integral part of the initial analog-to-digital conversion in the receiver. The Viterbi decoder implements a soft-decision algorithm to demodulate digital data from an analog signal corrupted by noise. Many ECC encoders/decoders can also generate a bit-error rate (BER) signal, which can be used as feedback to fine-tune the analog receiving electronics.

The maximum fractions of errors or of missing bits that can be corrected are determined by the design of the ECC code, so different error correcting codes are suitable for different conditions. In general, a stronger code induces more redundancy that needs to be transmitted using the available bandwidth, which reduces the effective bit-rate while improving the received effective signal-to-noise ratio. The noisy-channel coding theorem of Claude Shannon can be used to compute the maximum achievable communication bandwidth for a given maximum acceptable error probability. This establishes bounds on the theoretical maximum information transfer rate of a channel with some given base noise level. However, the proof is not constructive, and hence gives no insight of how to build a capacity achieving code. After years of research, some advanced ECC systems as of 2016[3] come very close to the theoretical maximum.

Forward error correction[edit]

In telecommunication, information theory, and coding theory, forward error correction (FEC) or channel coding[4][3] is a technique used for controlling errors in data transmission over unreliable or noisy communication channels. The central idea is that the sender encodes the message in a redundant way, most often by using an ECC.

The redundancy allows the receiver to detect a limited number of errors that may occur anywhere in the message, and often to correct these errors without re-transmission. FEC gives the receiver the ability to correct errors without needing a reverse channel to request re-transmission of data, but at the cost of a fixed, higher forward channel bandwidth. FEC is therefore applied in situations where re-transmissions are costly or impossible, such as one-way communication links and when transmitting to multiple receivers in multicast. FEC information is usually added to mass storage (magnetic, optical and solid state/flash based) devices to enable recovery of corrupted data, is widely used in modems, is used on systems where the primary memory is ECC memory and in broadcast situations, where the receiver does not have capabilities to request re-transmission or doing so would induce significant latency. For example, in the case of a satellite orbiting Uranus, a re-transmission because of decoding errors would create a delay of at least 5 hours.

FEC processing in a receiver may be applied to a digital bit stream or in the demodulation of a digitally modulated carrier. For the latter, FEC is an integral part of the initial analog-to-digital conversion in the receiver. The Viterbi decoder implements a soft-decision algorithm to demodulate digital data from an analog signal corrupted by noise. Many FEC coders can also generate a bit-error rate (BER) signal which can be used as feedback to fine-tune the analog receiving electronics.

The maximum proportion of errors or missing bits that can be corrected is determined by the design of the ECC, so different forward error correcting codes are suitable for different conditions. In general, a stronger code induces more redundancy that needs to be transmitted using the available bandwidth, which reduces the effective bit-rate while improving the received effective signal-to-noise ratio. The noisy-channel coding theorem of Claude Shannon answers the question of how much bandwidth is left for data communication while using the most efficient code that turns the decoding error probability to zero. This establishes bounds on the theoretical maximum information transfer rate of a channel with some given base noise level. His proof is not constructive, and hence gives no insight of how to build a capacity achieving code. However, after years of research, some advanced FEC systems like polar code[3] achieve the Shannon channel capacity under the hypothesis of an infinite length frame.

How it works[edit]

ECC is accomplished by adding redundancy to the transmitted information using an algorithm. A redundant bit may be a complex function of many original information bits. The original information may or may not appear literally in the encoded output; codes that include the unmodified input in the output are systematic, while those that do not are non-systematic.

A simplistic example of ECC is to transmit each data bit 3 times, which is known as a (3,1) repetition code. Through a noisy channel, a receiver might see 8 versions of the output, see table below.

| Triplet received | Interpreted as |

|---|---|

| 000 | 0 (error-free) |

| 001 | 0 |

| 010 | 0 |

| 100 | 0 |

| 111 | 1 (error-free) |

| 110 | 1 |

| 101 | 1 |

| 011 | 1 |

This allows an error in any one of the three samples to be corrected by «majority vote», or «democratic voting». The correcting ability of this ECC is:

- Up to 1 bit of triplet in error, or

- up to 2 bits of triplet omitted (cases not shown in table).

Though simple to implement and widely used, this triple modular redundancy is a relatively inefficient ECC. Better ECC codes typically examine the last several tens or even the last several hundreds of previously received bits to determine how to decode the current small handful of bits (typically in groups of 2 to 8 bits).

Averaging noise to reduce errors[edit]

ECC could be said to work by «averaging noise»; since each data bit affects many transmitted symbols, the corruption of some symbols by noise usually allows the original user data to be extracted from the other, uncorrupted received symbols that also depend on the same user data.

- Because of this «risk-pooling» effect, digital communication systems that use ECC tend to work well above a certain minimum signal-to-noise ratio and not at all below it.

- This all-or-nothing tendency – the cliff effect – becomes more pronounced as stronger codes are used that more closely approach the theoretical Shannon limit.

- Interleaving ECC coded data can reduce the all or nothing properties of transmitted ECC codes when the channel errors tend to occur in bursts. However, this method has limits; it is best used on narrowband data.

Most telecommunication systems use a fixed channel code designed to tolerate the expected worst-case bit error rate, and then fail to work at all if the bit error rate is ever worse.

However, some systems adapt to the given channel error conditions: some instances of hybrid automatic repeat-request use a fixed ECC method as long as the ECC can handle the error rate, then switch to ARQ when the error rate gets too high;

adaptive modulation and coding uses a variety of ECC rates, adding more error-correction bits per packet when there are higher error rates in the channel, or taking them out when they are not needed.

Types of ECC[edit]

A block code (specifically a Hamming code) where redundant bits are added as a block to the end of the initial message

A continuous code convolutional code where redundant bits are added continuously into the structure of the code word

The two main categories of ECC codes are block codes and convolutional codes.

- Block codes work on fixed-size blocks (packets) of bits or symbols of predetermined size. Practical block codes can generally be hard-decoded in polynomial time to their block length.

- Convolutional codes work on bit or symbol streams of arbitrary length. They are most often soft decoded with the Viterbi algorithm, though other algorithms are sometimes used. Viterbi decoding allows asymptotically optimal decoding efficiency with increasing constraint length of the convolutional code, but at the expense of exponentially increasing complexity. A convolutional code that is terminated is also a ‘block code’ in that it encodes a block of input data, but the block size of a convolutional code is generally arbitrary, while block codes have a fixed size dictated by their algebraic characteristics. Types of termination for convolutional codes include «tail-biting» and «bit-flushing».

There are many types of block codes; Reed–Solomon coding is noteworthy for its widespread use in compact discs, DVDs, and hard disk drives. Other examples of classical block codes include Golay, BCH, Multidimensional parity, and Hamming codes.

Hamming ECC is commonly used to correct NAND flash memory errors.[5]

This provides single-bit error correction and 2-bit error detection.

Hamming codes are only suitable for more reliable single-level cell (SLC) NAND.

Denser multi-level cell (MLC) NAND may use multi-bit correcting ECC such as BCH or Reed–Solomon.[6][7] NOR Flash typically does not use any error correction.[6]

Classical block codes are usually decoded using hard-decision algorithms,[8] which means that for every input and output signal a hard decision is made whether it corresponds to a one or a zero bit. In contrast, convolutional codes are typically decoded using soft-decision algorithms like the Viterbi, MAP or BCJR algorithms, which process (discretized) analog signals, and which allow for much higher error-correction performance than hard-decision decoding.

Nearly all classical block codes apply the algebraic properties of finite fields. Hence classical block codes are often referred to as algebraic codes.

In contrast to classical block codes that often specify an error-detecting or error-correcting ability, many modern block codes such as LDPC codes lack such guarantees. Instead, modern codes are evaluated in terms of their bit error rates.

Most forward error correction codes correct only bit-flips, but not bit-insertions or bit-deletions.

In this setting, the Hamming distance is the appropriate way to measure the bit error rate.

A few forward error correction codes are designed to correct bit-insertions and bit-deletions, such as Marker Codes and Watermark Codes.

The Levenshtein distance is a more appropriate way to measure the bit error rate when using such codes.

[9]

Code-rate and the tradeoff between reliability and data rate[edit]

The fundamental principle of ECC is to add redundant bits in order to help the decoder to find out the true message that was encoded by the transmitter. The code-rate of a given ECC system is defined as the ratio between the number of information bits and the total number of bits (i.e., information plus redundancy bits) in a given communication package. The code-rate is hence a real number. A low code-rate close to zero implies a strong code that uses many redundant bits to achieve a good performance, while a large code-rate close to 1 implies a weak code.

The redundant bits that protect the information have to be transferred using the same communication resources that they are trying to protect. This causes a fundamental tradeoff between reliability and data rate.[10] In one extreme, a strong code (with low code-rate) can induce an important increase in the receiver SNR (signal-to-noise-ratio) decreasing the bit error rate, at the cost of reducing the effective data rate. On the other extreme, not using any ECC (i.e., a code-rate equal to 1) uses the full channel for information transfer purposes, at the cost of leaving the bits without any additional protection.